近日,RISC-V指令集架构在全球半导体产业聚光灯下再一次强势破圈!

据路透社3月4日报道,中国计划首次发布指导意见,推动全国范围使用开源RISC-V芯片,加速RISC-V技术产业化进程。与此同时,欧洲高性能计算机构 (HPC) 联合企业启动DARE项目,计划投入2.4亿欧元,开发用于RISC-V架构的AI芯片及软件。

历经15年的发展,RISC-V正以惊人的速度改变着全球半导体行业的格局。从阿里达摩院即将交付的高性能处理器C930,到芯来科技在AI和汽车电子领域的进展,再到微核芯高性能服务器芯片的突破,RISC-V正在引领一场技术革命。这场革命不仅体现在性能的飞跃,更在于其开放、自由的特性,为无数创新者提供了前所未有的机遇。

一、升维战为何选择RISC-V?

处理器架构的产业演进始终遵循“场景驱动技术”的铁律。20世纪70年代末,英特尔以x86架构构建PC时代算力底座,奠定四十年产业根基;21世纪初在移动互联网浪潮中,ARM凭借能效优先的架构哲学,开创移动终端处理器新纪元。

然而,这两大体系虽主导市场已久,却埋下双重结构性矛盾。在产业层面,指令集标准垄断导致“硬件定义软件”的生态逆向,用户需要修改需求适配处理器,场景化应用的优化力度有限;在技术层面,全场景覆盖需求产生了功耗冗余等大量成本冗余。

当计算范式迈入云原生与AI大模型主导的新阶段,架构革新迎来三重突破窗口。异构计算催生CPU与AI加速器的动态协同需求,行业场景细化倒逼架构设计颗粒度提升2-3个数量级。在此背景下,RISC-V开放指令集展现出破局潜力:其模块化架构支持从AI推理单元到领域专用处理器的敏捷定制,更通过开源生态打破指令集架构长达四十年的标准垄断。Omdia预测,2024年至2030年期间,基于RISC-V的处理器出货量将以每年近50%的速度增长,预计到2030年出货量将达到170亿颗,占据全球市场近四分之一的份额。

值得注意的是,我国半导体产业在这场架构革命中展现出独特的战略路径。2020年成立的北京微核芯科技有限公司(以下简称:微核芯)正是其中典范。彼时,全球RISC-V开发者90%聚焦低端AIoT市场,而这家中国芯前瞻性锁定服务器与AI计算两大高端赛道——这恰是突破海外技术封锁的关键战场,也是实现架构自主可控的必争之地。

二、技术积累与创新突破的二重奏

在半导体行业,每一代架构突破都需要几十年的经验沉淀。微核芯团队凝聚二十余年产业know-how,成功实现从技术并跑到实现跨越,其自主研发的高性能处理器SPEC CPU2006分值达15分/GHz,性能比肩ARM最新的服务器芯片N2。

据介绍,这支团队在技术上涵盖高性能处理器开发的各个领域,包括架构设计、验证、物理实现和软件等全过程。因此,他们有足够的能力提供”全家桶”式的服务器系统方案,高性能CPU核+片上网络(NoC)多核互连+SoC架构,同时结合 Chiplet技术,大大降低了芯片的设计制造成本,加快芯片研发迭代速度。

图源:微核芯

以GKG系列产品为例,这款高性能RISC-V芯片集成多个自主研发的高性能处理器核,采用乱序多发射超标量流水线,在RISC-V基础指令集的基础上,支持硬件虚拟化、向量、AI等高性能指令集扩展,具有高性能、低功耗等优势,在服务器、终端设备、嵌入式装备和工业控制等领域完成规模化商用部署,彰显出RISC-V架构在高性能计算场景的创新潜力。

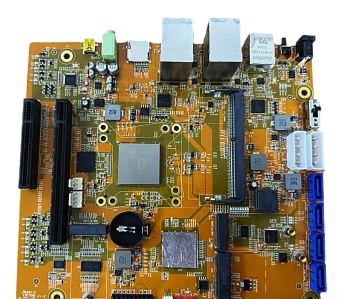

图源:微核芯

在微核芯看来,这些成就的背后,是两大核心能力的持续进化:

其一是”全局优化”能力:独到的架构设计与工艺演进协同的能力,从芯片架构设计到工艺实现全程自主把控,这样能做出更优功耗、更强性能的芯片,同时使开发周期大大缩短。

其二则是”量体裁衣”能力:根据客户具体需求定制芯片架构,统一优化分解各阶段的任务指标,通过合理调度资源,充分发挥工艺的性能、确保处理器的性能具备足够的竞争力。

正因如此,微核芯在短短几年便形成了技术护城河,已申请70多项中国发明专利,还在美国、欧洲等地拿到多个核心专利的授权。

图源:微核芯

凭借深厚的技术积累,微核芯还不断完善定制化服务,推出了RISC-V高性能处理器定制平台。该平台涵盖RISC-V高性能处理器核、片上网络(NoC)多核互连、SoC架构和软件平台,可以向用户提供全面的软硬件统一优化的最佳芯片方案。其中关键的高性能理器核,NoC多核互连以及SoC架构全部自研,支持多种性能级别的定制化,可根据用户需求进行深度优化。RISC-V高性能平台的应用领域广泛,适用于数据中心服务器、机器人、自动驾驶、高密度算力集群等众多领域。

三、突进X86/ARM的技术无人区

技术创新浪潮在向产业化高地突围过程中,必将遭遇商业化落地的挑战。显然,微核芯已做好应对准备,他们采取与应用深度结合的策略,要去做“X86和ARM想做,又做不了的事。”

当前RISC-V架构实现规模化商用的核心挑战聚焦于两大维度,其突破路径系统化呈现为:生态信任体系的构建工程和差异化赛道的精准突破策略。

具体而言,生态信心的建立可通过政策协同机制、技术验证闭环、产业协作网络等方面进行构筑。差异化赛道的突破则可瞄准算力重构机遇、新兴领域卡位,以及需求驱动开发。这也是微核芯不断探索出的商业化路径:通过构建政策引导、企业主导、院校支撑的立体化生态体系,在智能计算、汽车电子、工业自动化等万亿级市场形成突破态势。核心要素在于精准把握X86和ARM架构的刚性需求缺口,将RISC-V的架构自由度转化为场景适配优势,最终实现从技术优势到商业价值的闭环转化。

四、在AI算力深水区掀起海啸

如今,AI技术浪潮席卷全球,算法革新加速突破、应用场景深度渗透至核心业务领域,如何构建面向AI时代的系统性战略框架,已成为企业战略规划的关键命题。

在普适技术的演进图谱中,RISC-V与AI技术呈现显著共性特征——二者均属于底层架构型创新,其真正价值释放需通过垂直场景的深度结合来实现。面对国内半导体产业在先进制程与生态链上的代际差距,微核芯选择聚焦于场景驱动的架构创新。以人形机器人领域为例,其技术需求矩阵包含三个核心维度:能效约束、实时多模态交互以及认知智能实现。现有通用计算架构难以满足此类复合型技术指标,这正是RISC-V开放指令集与AI加速架构协同创新的机遇窗口。

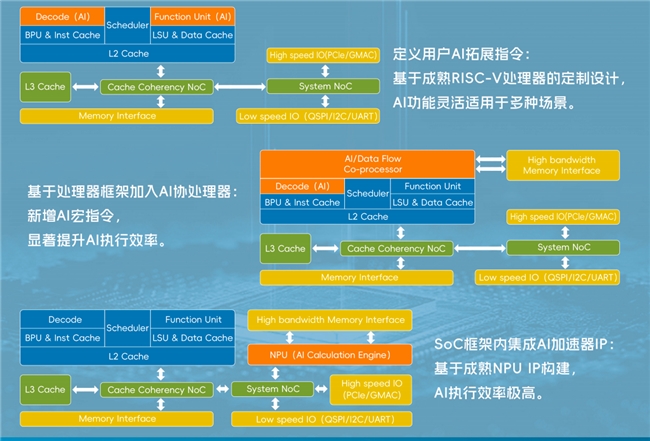

图源:微核芯

AI芯片的发展需要根据应用需求,合理优化定制芯片在通用和专用之间达到平衡。 微核芯指出传统架构中的割裂:CPU执行的是控制流,AI(或GPGPU)执行的是数据流;但在实际应用中没有绝对的数据流,也没有绝对的控制流,更多的是两者的结合以及面向不同领域的不同配比。任务的分解和调度是决定芯片系统解决方案的关键,需要应用和芯片设计的深度绑定才能实现,因此必须要设计好CPU与AI的协同框架。同时,软硬件协同框架尤为重要,需要从应用角度出发,对应用和计算框架、数据流和控制流进行深入分解。

微核芯为此提出了三个层次的CPU+AI协同框架:

方案1:SoC框架内AI加速模块的集成;

方案2:CPU层面的AI指令扩展;

方案3:CPU框架内AI协处理器设计。

在现有市场,芯片方案多数采用方案1与方案2,第1方案的AI执行效率高,但应对未来应用的适应性较差,而且与控制流的结合较弱,与CPU只能在内存层面进行交互。方案2的应用适应性最佳,但是AI执行效率最低,局限于控制流为主、数据流为辅的特殊应用领域。第3方案是基于高性能CPU的框架,保留了高性能CPU控制流执行能力强的特点,且能够结合AI协处理器AI执行效率高的优势,微核芯认为这才是未来AI芯片的发展趋势。

芯火燎原处,征途正当时!

中国工程院院士倪光南预见的RISC-V 架构革命浪潮已至,在这场重绘全球算力版图的征途中,微核芯正以中国智慧锻造RISC-V新内核。基于其深厚的技术积累、创新的技术路线和清晰的战略规划,微核芯既要做技术深水区的破冰者,更当产业升维战的领航员。

皖公网安备 34011102002444号

皖公网安备 34011102002444号